Contrairement au PXA270, le processeur PXA255 n'a pas d'interface d'acquisition vidéo. Pour traiter des flux vidéo avec une latence minimale, il faut en principe utiliser un capteur CMOS cadencé par un oscillateur dédié, contrôlé par le bus I2C, remplissant à débit constant une FIFO dont la sortie serait connectée au bus mémoire du processeur. Un exemple est décrit de façon détaillée dans [FS2006].

Ce document propose une solution plus simple et plus économique (mais moins fiable dans certains cas) reposant sur l'observation qu'un capteur CMOS fonctionne raisonnablement bien avec une horloge non périodique.

cfstix. Nous n'utiliserons pas les spécificités de CompactFlash. Seuls nous intéressent le connecteur Hirose 92 points, les buffers sur les bus d'adresses et de données, et le connecteur au pas de 1,27 mm.

Avertissement

Ne connectez pas un capteur CMOS au port CF d'une carte netcf ou wifistix-cf, car les sorties ne sont pas trois-états et seraient donc en conflit avec celles du circuit LAN91C111 ou du module Wi-Fi.

Un connecteur CF femelle. Sources possibles :

connecteur CF standard (difficile à acheter à l'unité) ;

à partir d'une carte CF défectueuse ;

connecteur femelle générique 2x25x1,27 mm (non conforme à la norme CF, mais suffisamment compatible).

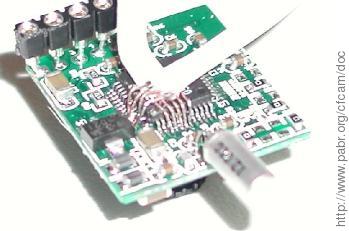

Un capteur CMOS monté sur un circuit imprimé. Sources possibles :

démonter une webcam USB (modèles testés : SN9C102+OV7630 et SN9C120+HV7131R) ;

C3088/C3188 avec horloge externe (non testés) ;

Connecter GND au USB_GND de la caméra.

Connecter V_BATT (+5 V) au USB_VBUS de la caméra.

Connecter nPIOR à SEN_CLK (également dénommé MCLK).

Connecter S_IMG[0..8] à XMD[0..8].

Désactiver /etc/init.d/S30pcmcia.

Activer SKTSEL : pxa_gpio_mode(GPIO54_pSKTSEL_MD).

Activer le décodage de la plage d'adresses PCMCIA : MECR=MECR_CIT.

Programmer les timings I/O : MCIO(0)=0 fonctionne; MCIO(0)=(10<<14)|(5<<7)|10 donnerait une marge de sécurité supplémentaire.

Transférer par DMA quelques mégaoctets à partir de 0x2000000 (slot 0), en mode WIDTH2|BURST4.

Decoder les données brutes. En pratique il s'agit de supprimer les synchros horizontales et verticales et de reconstruires les couleurs à partir d'une image Bayer.

La documentation des contrôleurs mémoire et DMA est dans [PXA255_DEVEL].

[PXARC] contient une implémentation complète de cette approche.

Le système fonctionne de la façon suivante :

Tant que le SN9C1xx ne détecte pas d'hôte USB, il reste en veille avec SEN_CLK en haute impédance.

Dans sa configuration par défaut, le capteur est capable de produire des images. Sinon, nous devrions le configurer à l'aide d'I2C.

Chaque lecture à l'adresse 0x20000000 génère une impulsion sur SEN_CLK. Bien que les accès DMA se déroulent en rafales, ceci suffit à cadencer le capteur.

Figure 3. Données brutes d'une capture DMA (un mot de 16 bit sur deux, décalés d'un bit vers la droite)

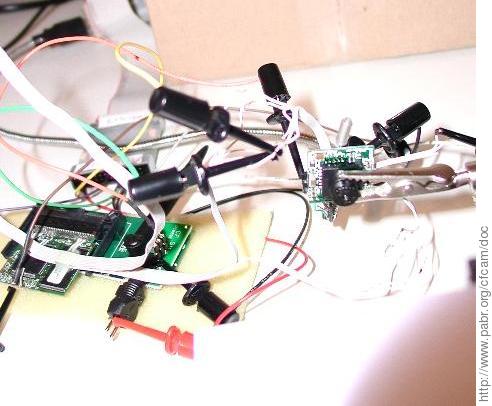

Les performances sont limitées par la complexité du cycle de lecture CF/PCMCIA. Un prototype (Figure 5, « Une autre webcam modifiée (SN9C120+HV7131R) ») atteint 320x240x14im/s et 640x480x4im/s. Avec un capteur CMOS générant un pixel par cycle d'horloge, on devrait obtenir 320x240x28im/s et 640x480x8im/s (soit 3,8 M pixels/s, intervalles de synchro compris). À titre de comparaison, l'interface de capture vidéo du PXA270 peut cadencer des capteurs jusqu'à 52 MHz.

La figure ci-dessous montre un effet indésirable de ce faible débit lorsque le capteur est de type rolling shutter : la déformation des objets mobiles est très prononcée.

[PXARC] pxaRC - Logiciels pour le modélisme et la robotique sur Linux/PXA255/PXA270 . http://www.pabr.org/pxarc/doc/pxarc.fr.html .

[FS2006] Linux Robot with Omnidirectional Vision. http://cswww.essex.ac.uk/mv/omnipapers/gwfran06with-header.pdf.